According to McKinsey & Company, semiconductor companies can lose millions of dollars through yield losses. Yield losses are the losses that occur due to defects, rework, or scrap in the output of a machine or a process.

There are many ways semiconductor manufacturers can improve quality and output. However, given how complex and costly the manufacturing of integrated circuits can be, it is critical to strive for continuous improvement.

Quality Control and Yield

Several hundred chips are fabricated simultaneously on a wafer. We are not talking about delicious cookies; a wafer is typically a piece of silicon (one of the most abundant semiconductors available worldwide) or other semiconductor material, designed in the form of a very thin disc. Wafers are used to create electronic integrated circuits.

Wafers are processed together in groups called lots. Once the fabrication process is complete, each chip on every wafer is subjected to a series of functionality tests and is declared to be either good or defective.

After testing, analysis of the data for quality control and process-monitoring purposes typically focuses on overall lot level summary measures such as yield (the number of good chips in a lot) and the good-to-functional ratio (the number of good chips in a lot divided by the number of chips that work but do not meet specification limits).

While these measures are critical, they also assume that defects are distributed randomly both within and across wafers in the lot.

Minitab Understands the Growing Needs of the Semiconductor Industry

How the Wafer Map Can Help

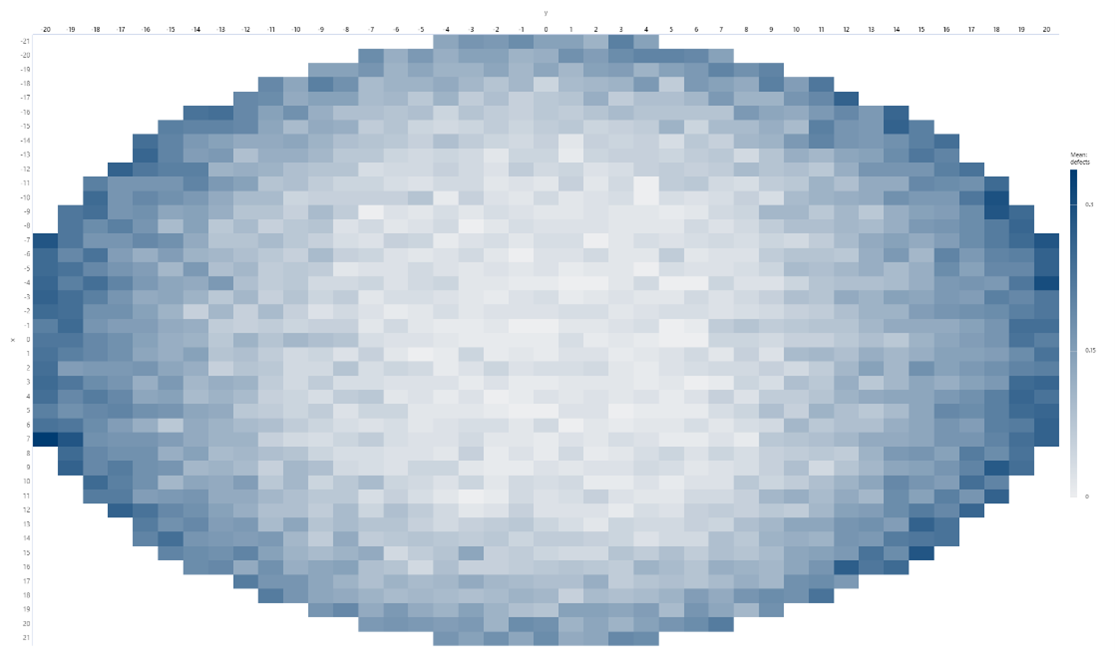

Understanding the lot level yield and analyzing root causes is the key to driving yield improvements. To gain deeper insights, by using a wafer map, an engineer can visualize whether or not defective chips display a systematic pattern or cluster.

These spatial patterns may contain useful information about potential manufacturing problems that is missed by overall summary measures. According to Mark H. Hansen, Vijayan N. Nair and David J. Friedman who co-wrote the article “Monitoring Wafer Map Data from Integrated Circuit Fabrication Processes for Spatially Clustered Defects,” specific patterns may point to common problems. For example, if you see a ring of dead chips around the edge of the wafer, this may indicate an uneven temperature distribution during the rapid thermal annealing process. A checkerboard pattern of defective chips often indicates a malfunctioning stepper. Excess vibration in a machine may liberate enough particles to cause all the chips in some contiguous region of a wafer to fail. In general, clusters of defects can be classified as either particle or process related, with particle-related clusters being assignable to individual machines and process related clusters being attributable to one or more process steps not meeting specification requirements.

Above is an example of a wafer map – the ring of defects may suggest an uneven temperature distribution. In MSS

On the other hand, spatially random defects also may tell a story. For example, random defect densities tend to rise and fall with the overall cleanliness of the cleanroom. These can be reduced through a continuous improvement program of long-term, gradual improvement or perhaps by updating and upgrading equipment overhaul. Alternatively, spatially random defects may indicate that there is no problem with the process, but rather the materials.

The Wafer Map – An Important Quality Tool

Quality control in a complex manufacturing environment is complex too. Due to the costly nature of semiconductor manufacturing, any additional insights that can improve yield can drive significant cost savings. The Wafer Map is an additional tool in the quality engineer’s toolkit to identify root causes of problems faster.

Try it for yourself! Get a free 30 day trial of Minitab Statistical Software.

Be the first to comment